## Semiconductor Devices: Theory and Application

Laboratory Manual

James M. Fiore

## Semiconductor Devices: Theory and Application

## Laboratory Manual

by

James M. Fiore

Version 1.4.7, 11 March 2021

Laboratory Manual for Semiconductor Devices: Theory and Application

This Laboratory Manual for Semiconductor Devices: Theory and Application, by James M. Fiore is copyrighted under the terms of a Creative Commons license:

This work is freely redistributable for non-commercial use, share-alike with attribution

Published by James M. Fiore via dissidents

ISBN13: 978-1796601947

For more information or feedback, contact:

James Fiore, Professor Electrical Engineering Technology Mohawk Valley Community College 1101 Sherman Drive Utica, NY 13501 jfiore@mvcc.edu

For the latest revisions, related titles, and links to low cost print versions, go to: <u>www.mvcc.edu/jfiore</u> or my mirror sites <u>www.dissidents.com</u> and <u>www.jimfiore.org</u>

YouTube Channel: <u>Electronics with Professor Fiore</u>

Cover art, Ride, by the author

#### Introduction

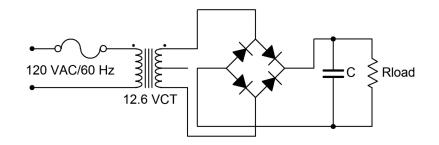

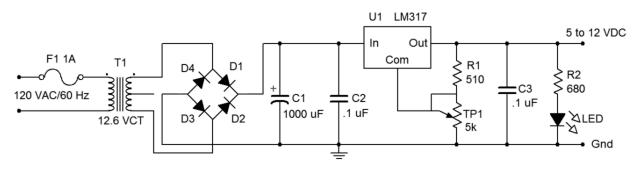

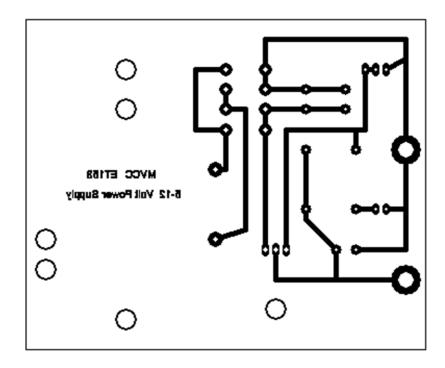

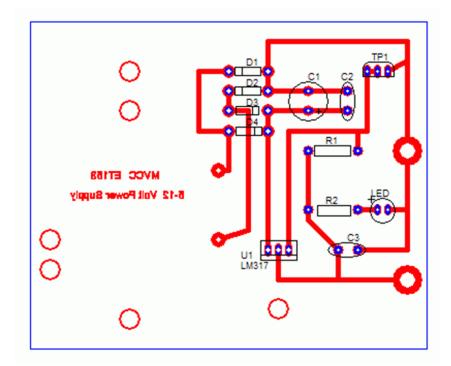

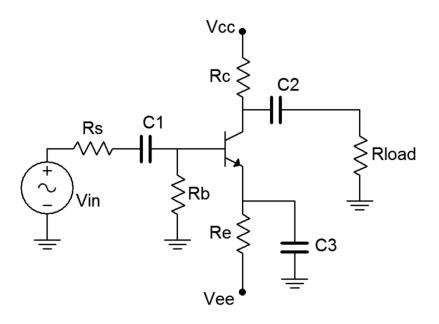

This laboratory manual is the companion to my OER text Semiconductor Devices: Theory and Application. It is intended for use in introductory semiconductor devices courses and is appropriate for two and four year electrical engineering technology curriculums. The manual contains sufficient exercises for two 15 week courses using a two to three hour practicum period. It assumes familiarity with basic electrical circuit analysis techniques and theorems. The topics cover basic diodes through DC biasing and AC analysis of small signal bipolar and FET amplifiers along with class A and B large signal analysis. For equipment, each lab station should include a dual adjustable DC power supply, a dual trace oscilloscope, a function generator and a quality DMM. Some exercises also make use of a distortion analyzer and a low distortion generator (generally, THD below 0.01%), although these portions may be bypassed. For components, a selection of standard value  $\frac{1}{4}$  watt carbon film resistors ranging from a few ohms to a few mega ohms is required along with an array of typical capacitor values (film types recommended below 1 μF and aluminum electrolytics above). Specialty passives include a CdS cell, thermistor and a 20 ohm 20 watt load resistor. A decade resistance box and a 10 k $\Omega$  potentiometer may also be useful. Active devices include small signal diodes such as the 1N914 or 1N4148, rectifying diodes such as the 1N4000 series, the NZX5V1B or 1N751 Zener, single LEDs of various colors, a super bright LED, 2N3904 or 2N2222 NPN transistor, 2N3906 PNP transistor, and MPF102 N channel JFET. A small 12.6 VCT power transformer is used in the power supply project and associated exercises along with a three-terminal linear regulator.

Each exercise begins with an Objective and a Theory Overview. The Equipment List follows with space provided for serial numbers and measured values of components. Schematics are presented next along with the step-by-step procedure. Many exercises include sections on troubleshooting and design. Simulations are often presented as well, and any quality simulation package such as <u>LTspice</u>, <u>TINA-TI</u>, Multisim or PSpice can be used. All data tables are grouped together, typically with columns for the theoretical and experimental results, along with a column for the percent deviations between them. Finally, a group of appropriate questions are presented.

Other laboratory manuals in this OER series include DC and AC Electrical Circuit Analysis, Computer Programming with Python<sup>™</sup> and Multisim<sup>™</sup>, Operational Amplifiers & Linear Integrated Circuits, Embedded Controllers Using C and Arduino, and Science of Sound. OER texts for DC and AC Electrical Circuit Analysis, Embedded Controllers, and Operational Amplifiers & Linear Integrated Circuits are also available. Finally, this work supersedes the earlier "Laboratory Manual for Linear Electronics".

## A Note from the Author

This manual is used at Mohawk Valley Community College in Utica, NY, for our <u>ETAC of ABET</u> accredited AAS program in Electrical Engineering Technology. I am indebted to my students and colleagues for their support and encouragement of this project. It was created out of a desire to offer a minimal cost lab manual for our students that covered the requisite material and made optimal use of our laboratory facilities. While it would have been possible to seek a traditional publisher for this work, as a long-time supporter and contributor to freeware and shareware computer software, I have decided instead to release this title using a Creative Commons non-commercial, share-alike license. I encourage others to make use of this manual for their own work and to build upon it. If you do add to this effort, I would appreciate a notification. Please note that the latest versions of all texts and manuals in both PDF and easily editable versions (odt) may be found at my MVCC site or on my mirror site, <u>www.dissidents.com</u>

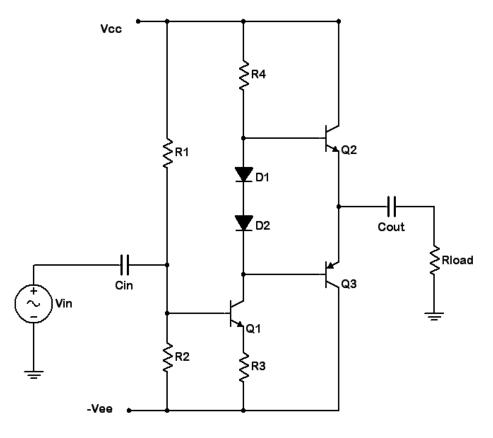

"It doesn't matter how beautiful your theory is, it doesn't matter how smart you are. If it doesn't agree with experiment, it's wrong."

- Richard Feynman

## Table of Contents

| 1. Introduction to Electronics       | Lab            |                 |           |           | 8          |

|--------------------------------------|----------------|-----------------|-----------|-----------|------------|

| 2. <u>Resistive Sensors</u> .        | •              |                 | •         | •         | 20         |

| 3. <u>Diode Curves</u> .             | •              |                 | •         | •         | 24         |

| 4. Light Emitting Diodes             | •              |                 | •         | •         | 30         |

| 5. <u>Photodiodes</u> .              | •              |                 |           |           | 36         |

| 6. <u>The Zener Diode</u> .          |                |                 |           | •         | 40         |

| 7. <u>The Oscilloscope</u> (four and | d two c        | hanne           | l versio  | ns)       | 46, 52, 60 |

| 8. Diode Clippers and Clamp          | <u>pers</u>    |                 | •         | •         | 68         |

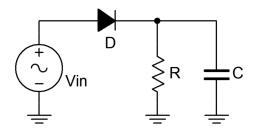

| 9. Half-wave Rectifier .             |                | •               |           | •         | 72         |

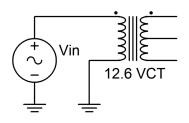

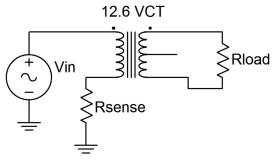

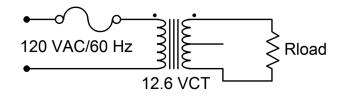

| 10. <u>The Transformer</u> .         |                |                 | •         | •         | 76         |

| 11. Full-wave Bridge Rectifier       |                |                 | •         | •         | 80         |

| 12. The DC Power Supply Proje        | <u>ect</u>     | •               |           | •         | 84         |

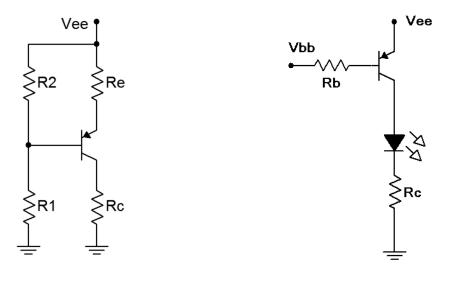

| 13. <u>Base Bias</u>                 |                | •               |           | •         | 90         |

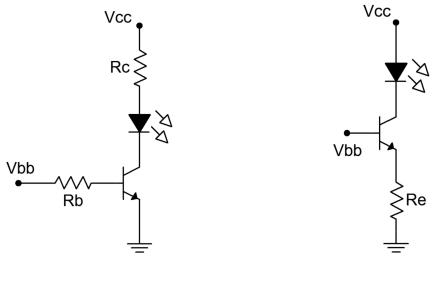

| 14. LED Driver Circuits .            |                | •               |           | •         | 96         |

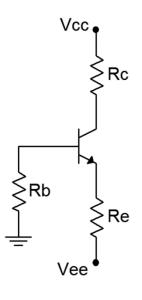

| 15. <u>Emitter Bias</u>              |                | •               |           | •         | 102        |

| 16. Voltage Divider Bias.            |                | •               |           | •         | 108        |

| 17. Feedback Biasing                 |                | •               |           | •         | 114        |

| 18. PNP Transistors                  |                | •               |           | •         | 120        |

| 19. Common Emitter Amplifier         |                |                 |           |           | 126        |

| 20. <u>Swamped CE Amplifier</u>      |                | •               |           | •         | 132        |

| 21. Frequency Limits .               |                | •               |           | •         | 138        |

| 22. Voltage Follower .               |                |                 | •         | •         | 142        |

| 23. <u>Class A Power Analysis</u>    |                | •               |           | •         | 148        |

| 24. <u>Class B Power Analysis</u>    | •              | •               |           |           | 154        |

| 25. Power Amp with Driver            |                | •               |           | •         | 160        |

| 26. <u>JFET Bias</u>                 |                |                 | •         | •         | 166        |

| 27. JFET Amplifiers .                |                |                 |           |           | 172        |

| 28. JFET Ohmic Region .              |                |                 |           |           | 178        |

|                                      |                |                 |           |           |            |

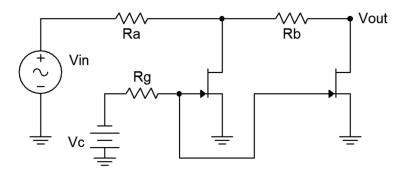

| Appendix A: Creating Graphs          | <u>: Using</u> | <u>a Sprea</u>  | adshee    | <u>et</u> | 182        |

| Appendix B: Manufacturer's E         | Datash         | <u>eet Link</u> | <u>(S</u> |           | 184        |

| Appendix C: Component Sym            | <u>nbol Gl</u> | ossary          |           | •         | 185        |

## Introduction to Electronics Lab

## Objective

The laboratory emphasizes the practical, hands-on component of this course. It complements the theoretical material presented in lecture, and as such, is integral and indispensible to the mastery of the subject. There are several items of importance here including proper safety procedures, required tools, and laboratory reports. This exercise will finish with a section on component identification.

## Lab Safety and Tools

If proper procedures are followed, the electrical lab is a perfectly safe place in which to work. There are some basic rules: No food or drink is allowed in lab at any time. Liquids are of particular danger as they are ordinarily conductive. While the circuitry used in lab normally presents no shock hazard, some of the test equipment may have very high internal voltages that could be lethal (in excess of 10,000 volts) along with the 120 VAC power used to operate the equipment that can also be lethal if good safety practices are not followed. Spilling a bottle of water or soda onto such equipment could leave the experimenter in the receiving end of a severe shock. Similarly, items such as books and jackets should not be left on top of the test equipment as it could cause overheating. Use caution in storing these items during lab periods to avoid trip or fall hazards in the lab.

Each lab bench is self contained. All test equipment is arrayed along the top shelf. Built into the bench is a power strip. All test equipment for this bench should be plugged into this strip. None of this equipment should be plugged into any other strip. This strip is controlled by a circuit breaker. In the event of an emergency, all test equipment may be powered off through this one switch. Further, the benches are controlled by dedicated circuit breakers in the main lab panel. Located at the front of the lab is an A/B/C class fire extinguisher suitable for electrical fires. Also at the front of the lab is a safety kit. This contains bandages, cleaning swaps and the like for small cuts and the like. Familiarize yourself with the location of these items in the lab. For serious injury, the Campus Security Office should be contacted.

A lab bench should always be left in a secure mode. This means that the power to each piece of test equipment should be turned off, the bench itself should be turned off, all AC and DC power and signal sources should be turned down to zero, and all other equipment and components properly stowed with lab stools pushed under the bench. Any cables or cords used in the lab should be stored properly after the exercise is completed.

It is important to come prepared to lab. This includes the class text, the lab exercise for that day, class notebook, calculator, and hand tools. The tools include an electronic breadboard, test leads, wirestrippers, and needle nose pliers or hemostats. A small pencil soldering iron may also be useful. A basic DMM (digital multimeter) rounds out the list.

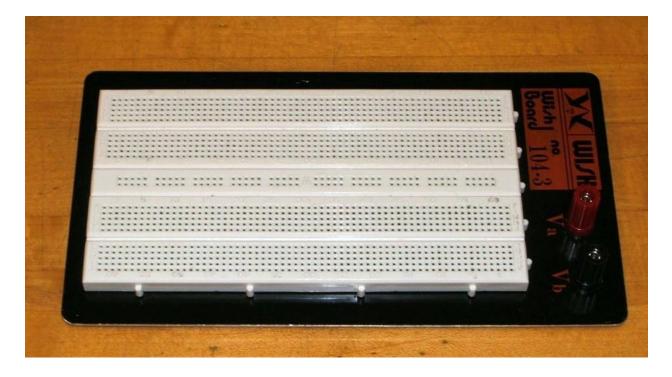

A typical breadboard or protoboard is shown below:

This particular unit features two main wiring sections with a common strip section down the center. Boards can be larger or smaller than this and may or may not have the mounting plate as shown. The connections are spaced 0.1 inch apart which is the standard spacing for many semiconductor chips. These are clustered in groups of five common terminals to allow multiple connections. The exception is the common strip which may have dozens of connection points. These are called *buses* and are designed for power and ground connections. Interconnections are normally made using small diameter solid hookup wire, usually AWG 22 or 24. Larger gauges may damage the board while smaller gauges do not always make good connections and are easy to break.

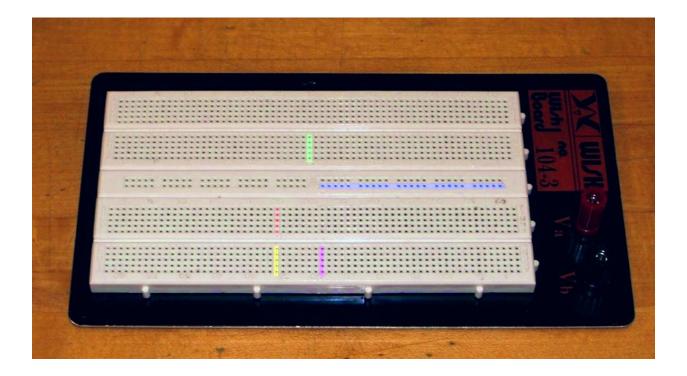

In the picture below, the color highlighted sections indicate common connection points. Note the long blue section which is a bus. This unit has four discrete buses available. When building circuits on a breadboard, it is important to keep the interconnecting wires short and the layout as neat as possible. This will aid both circuit functioning and ease of troubleshooting.

## Component Identification

In this lab, many different electronic components are used including passive devices such as resistors and capacitors as well as semiconductors such as diodes and transistors, and finally, integrated circuits. These devices are available in many different case styles. Two broad classifications are through-hole and surface mount. As circuits will be built on protoboards, through-hole components are of particular interest here. Surface mount devices are generally smaller and use thin flat tabs or stubs in place of ordinary wire leads. In production they are soldered directly to the surface of the printed circuit board without the use of holes.

#### **Resistors and Potentiometers**

Resistors are perhaps the single most common component. They are classified as passive devices (versus active devices AKA semiconductors). Resistors have two leads and are not directional so they cannot be inserted backwards. Leads are usually axial (i.e., emanating from opposite ends). The physical size of a resistor indicates its power handling capacity, not its resistance. The general purpose lab resistor is usually a carbon film type, <sup>1</sup>/<sub>4</sub> watt dissipation. Resistance values are shown via a color coded series of bands for most types, although high precision resistors may have the value printed directly on the body.

Potentiometers may be either rotary or linear travel (slider), with rotary being the most common. Most rotary pots are <sup>3</sup>/<sub>4</sub> turn, although precision trim pots may be 20 turns or more. Typically, the center of the three connections is the wiper arm. Rotary pots may be designed for panel mount (for example, a volume control on a stereo) or board mount (such as a calibration control). The taper of a pot indicates how resistance and position are related. Pots may have a linear taper or a specialized audio taper (log taper). A linear taper means that a specific degree of rotation will produce the same resistance change. Rotating the

shaft half way, for example, results in a 50/50 split of the resistance. In contrast, an audio taper pot would show a 10/90 split. Pots are also available in multi-gang, that is, several pots controlled by one common shaft.

Figure 1, Resistors and Potentiometers

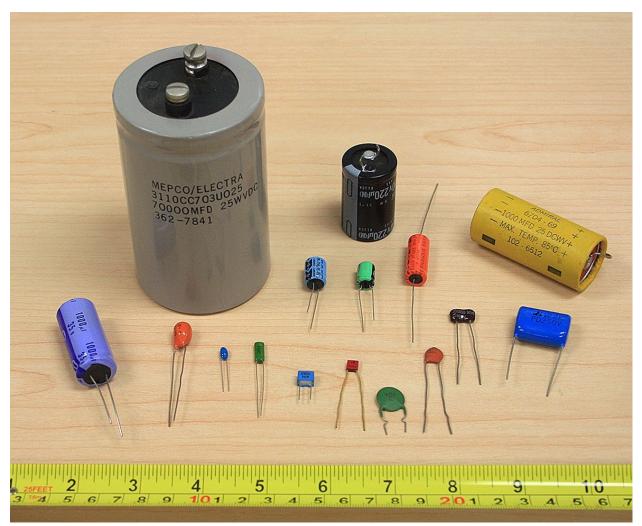

#### Capacitors

Capacitors are also classified as passives and can be though of as very short term energy storage devices. Capacitors are dual lead but may have either axial or radial (radiating from one end) leads. Unlike resistors, the physical size of a capacitor offers a clue as to its capacitance and voltage rating. All other factors being equal the greater the capacitance or voltage rating, the larger the capacitor. Most smaller capacitors (below 1  $\mu$ F) are not polarized and can be inserted into a circuit either way. The more popular dielectrics for this range include the ceramics (usually disk or coin shaped) and poly film types (polyester, polypropylene, etc.) which are usually block shaped. Teardrop shaped tantalum capacitors are used commonly for power supply bypass. They are polarized and must be inserted in the circuit in the specified direction. Larger capacitance values (over 1  $\mu$ F) are often realized via aluminum electrolytics. These are also polarized. Failure to insert these in the proper direction may result in unpredictable results, including the capacitor exploding. While they do not perform as well as film types in terms of leakage, accuracy, etc., they are offer high volumetric efficiency (i.e., small physical size given the capacitance). Very large caps may have screw terminals in place of wire leads. In years past, color coding was common but this has generally been replaced with values printed directly on the body of the capacitor. Sometimes a numeric code is used such as "102". This is read as 10 followed by 2 zeroes, with the result in picofarads, or 1000 pF (1 nF) in this case. Finally, because capacitors are charge storage devices, they may present a shock hazard from stored charge after they are removed from a circuit. This charge may be bled off with a low value resistance placed across the leads.

Figure 2, Capacitors

#### Inductors

The third and final passive device is the inductor. Also non-polarized, they normally have axial leads. Smaller values may be completely encapsulated and appear not much different from a carbon composition resistor. Others may use some form of jacket or coating while still others show bare wire (the wire only appears bare, it is in fact covered by a thin clear insulating coating). These vary from the size of small resistors to what appear to be large spools of wire.

Figure 3, Inductors

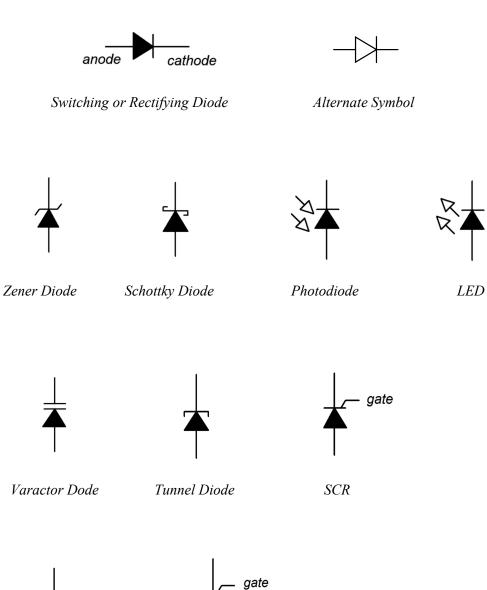

#### Diodes

Diodes are a two lead semiconductor. They are polarized and typically have axial leads. The two leads are referred to as the anode and cathode. Signal diodes are around the size of <sup>1</sup>/<sub>4</sub> watt resistors and sometimes use a glass body. The cathode is marked by a band or stripe on the body of the diode. The cathode of an LED is usually marked by a flat spot on the plastic housing or by the shorter of the two leads. High power diodes are much more robust and might appear at first glance to be a short bolt or stud with leads attached to it. Component numbers are usually stamped on the body of the device.

Figure 4, Diodes

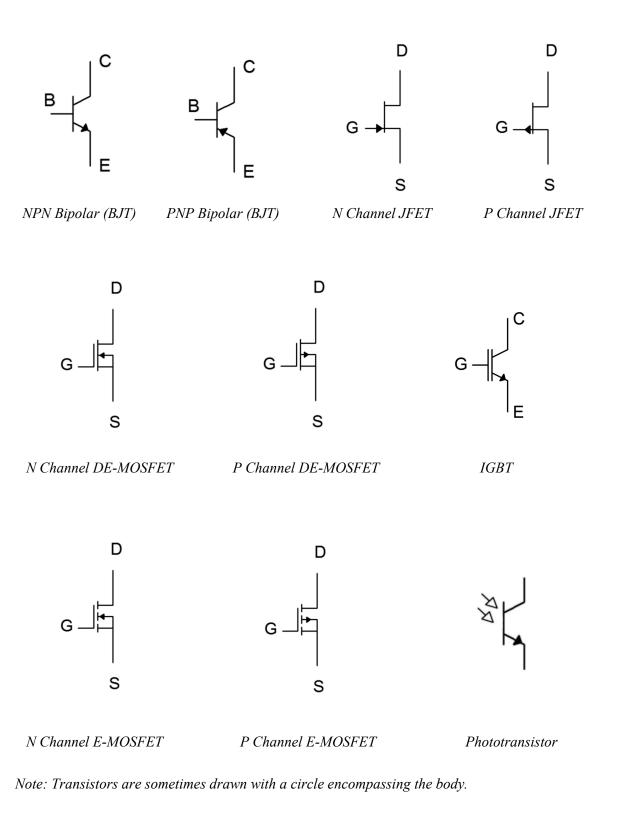

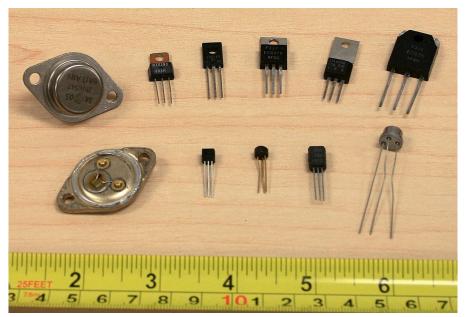

#### Transistors

There are many types of transistors. Generally, they are three lead devices. Component model numbers will be stamped directly onto the case. Small power dissipation (< 500 mW) units will usually be seen in plastic TO-92 cases, round metal TO-5 cans or variations on the theme. Mid power devices typically use TO-220, TO-202 or the like "power tab" cases. For higher powers the oval TO-3 cases are employed. A similarly shaped but slightly smaller variant is the TO-66. Power devices will need to use a heat sink to keep them cool. TO-92 cases use a flattened front face so that the three pins may be distinguished from each other without confusion. The round TO-5 can uses a small tab to indicate pin 1.

Figure 5, Transistors

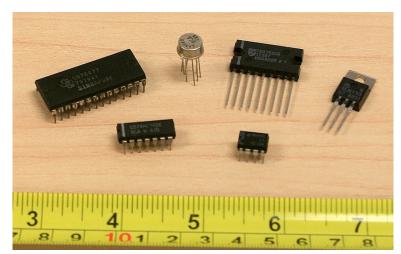

#### Integrated Circuits

There are a very wide variety of integrated circuits. Multi-lead versions of the TO-5 can are sometimes used but the most common through-hole package is the Dual In-Line Package, denoted as DIP or DIL. A single in-line package is also available for some functions. High power devices often use multi-lead versions of the popular TO-220 and TO-3 case styles. Like other semiconductors, component model numbers are printed directly on the package. A notch or dimple will denote which lead is pin 1 on the DIP/DIL cases.

Figure 6, Integrated Circuits

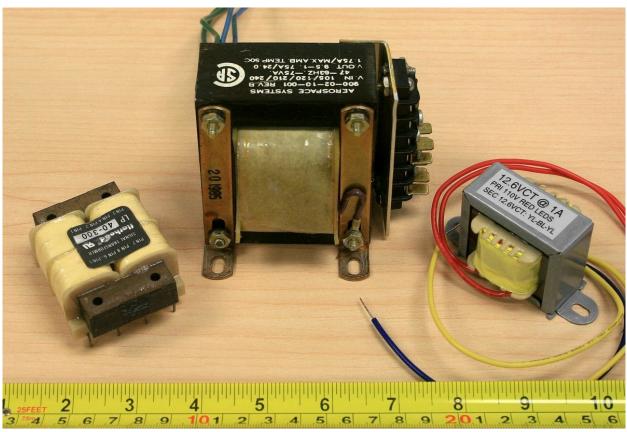

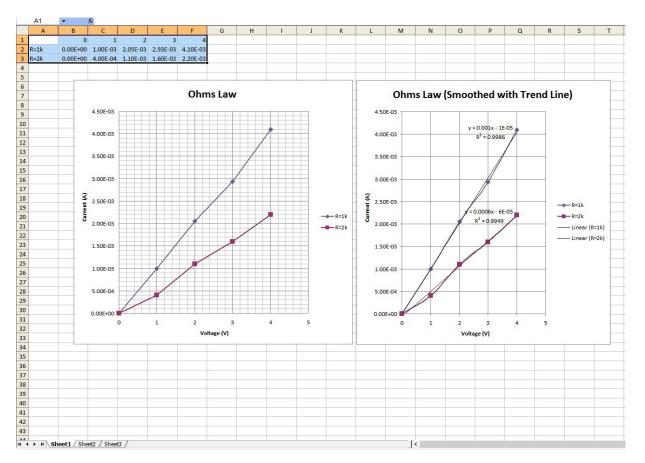

#### Transformers

Transformers can vary from tiny audio devices to room size devices used in power generation and distribution. No matter the size, their job is a simple one: to isolate the source and load, to match two different impedance devices or to change the voltage level. A very common application is stepping down a 120 VAC line voltage to a more modest level so that it can be rectified, filtered, and turned into a stable DC source to drive electronic circuits. Besides the voltage turns ratio, the most important characteristic is the VA or volt-amps rating of the device. All other factors being equal, the higher the VA rating, the larger the transformer. Transformers applicable for consumer electronics may be either chassis mount with leads or PCB mount with through-hole pins. Transformers **only** operate with AC voltages.

Figure 7, Transformers

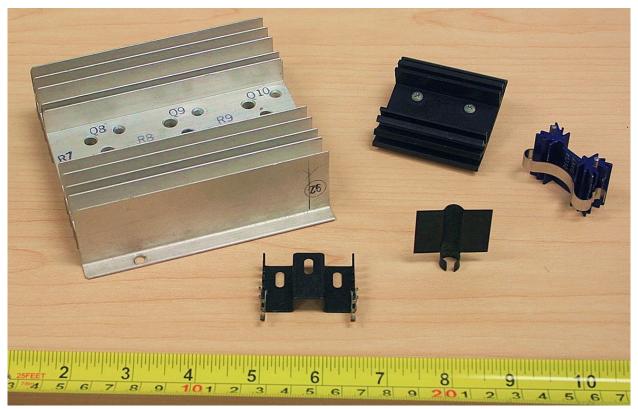

#### Heat Sinks

Heat sinks are not a device, per se, but they are essential tools of semiconductor heat management. Their job is to effectively move heat from the semiconductor's case to the surrounding air, keeping the semiconductor cool. They range in size from small clip-ons to large extruded aluminum finned plates. Some cases, such as the body of the TO-3 or the tab of the TO-220 are electrically live. To prevent possible shorts and a live chassis, non-conductive isolating tabs and grommets are used to attach the semiconductors to the heat sink.

Figure 8, Heat Sinks

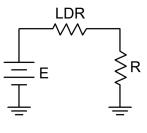

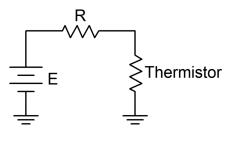

# 2 Resistive Sensors

## Objective

The objective of this exercise is to investigate devices that can be used to sense environmental factors such as light and temperature. These are important if circuitry is to react to surrounding conditions, for example, controlling fan speed that is proportional to temperature or turning lights on or off depending on existing light levels. Two such devices are the light dependent resistor or LDR, and the thermistor or temperature dependent resistor. They can be thought of as resistors whose values depend on either the surrounding light levels or the temperature.

## Theory Overview

One typical LDR is the CdS (Cadmium Sulfide) cell. The resistance of the CdS cell is inversely proportional to light levels. In darkness, it may exhibit a resistance of tens or even hundreds of kilo ohms. Under high brightness, the resistance may be as little as a few hundred ohms. Thermistors come in two types: PTC or Positive Temperature Coefficient whose resistive value increases with temperature, and NTC or Negative Temperature Coefficient whose resistance decreases with increasing temperature. In contrast, ordinary resistors are designed to be immune to temperature change as much as possible.

One way of using these devices is by placing them in a voltage divider. The resulting voltage will reflect the light levels or temperature. Depending on the position of the device, the voltage can be made to either increase or decrease as the environmental factor increases. For example, the voltage could rise as temperature rises but it could also be designed to have the voltage decrease as temperature rises. Both functions have their uses. Finally, it is worth noting that these devices do not necessarily respond immediately to environmental changes. For example, a thermistor might be used to sense air temperature. If the air temperature were to suddenly rise, there would be some time lag in the response of the thermistor. This is due to the fact that the thermistor itself has mass and requires some time to either heat up or cool down.

## Equipment

| (1) Adjustable DC power supply                               | model:  | srn: |  |  |

|--------------------------------------------------------------|---------|------|--|--|

| (1) DMM                                                      | model:  | srn: |  |  |

| (1) Non-diffuse light source (pen light)                     |         |      |  |  |

| (1) Heat source (diffused light duty heat gun or blow dryer) |         |      |  |  |

| (1) Nominal 1 k $\Omega$ – 10 k $\Omega$ CdS cell (GL5528)   |         |      |  |  |

| (1) 10 k $\Omega$ @ 25°C NTC thermistor (Vishay NTCLE100E3)  |         |      |  |  |

| (1) 10 k $\Omega$ resistor $\frac{1}{4}$ watt                | actual: |      |  |  |

|                                                              |         |      |  |  |

CdS cell datasheet: <u>http://cdn.sparkfun.com/datasheets/Sensors/LightImaging/SEN-09088.pdf</u> Thermistor datasheet: <u>http://www.vishay.com/docs/29049/ntcle100.pdf</u>

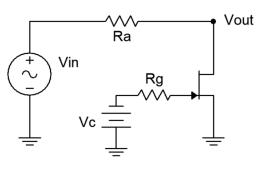

## **Schematics**

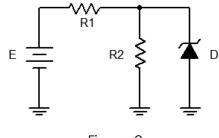

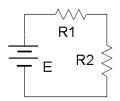

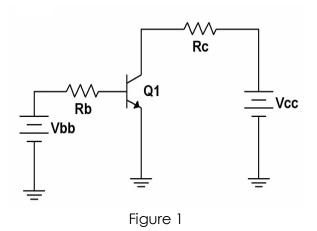

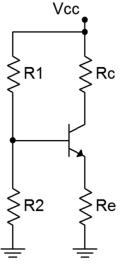

Figure 1

Figure 2

## Procedure

#### LDR

- Use the DMM to measure the resistance of the LDR. Do this away from any windows and do not block ambient room lighting from hitting the device. Record the resistance value in Table 1 under "Normal".

- 2. Place a finger over the LDR to block all light, making sure that the leads are not also touched. Record the resulting resistance value under "Dark".

- 3. Shine the pen light directly onto the LDR at a distance of about 25 centimeters. Record the result under "Bright".

- 4. Construct the circuit of Figure 1 using E=10 volts and  $R=10 \text{ k} \Omega$ . Using the voltage divider rule, determine the expected value for the voltage across R under normal lighting and then measure the voltage. Record these values in Table 2.

- 5. Repeat step 4 for the Dark and Bright conditions.

- 6. Finally, slowly move the pen light toward and away from the LDR. Note what happens to the voltage, recording the maximum and minimum voltages obtained in Table 3.

#### Thermistor

- Use the DMM to measure the resistance of the LDR at room temperature and record the result in Table

Do not handle the device excessively as body heat may affect it.

- 8. Build the circuit of Figure 2 using E=10 volts and  $R=10 \text{ k}\Omega$ . Measure the voltage across the thermistor and record it in Table 5 under "Room Temp".

- 9. Monitor the thermistor voltage while applying heat. Caution: If you are using a standard heat gun, place it on a low setting, use a diffuser or keep the gun at least a half meter away to avoid possibly damaging connecting wires or the protoboard. After 30 to 60 seconds, record the thermistor voltage in Table 5. Turn off the heat source and note how long it takes the thermistor circuit to recover back to the original reading.

## Data Tables

| Variation | Resistance |

|-----------|------------|

| Normal    |            |

| Dark      |            |

| Bright    |            |

Table 1

| Variation | V <sub>R</sub> Theory | V <sub>R</sub> Experiment | % Deviation |

|-----------|-----------------------|---------------------------|-------------|

| Normal    |                       |                           |             |

| Dark      |                       |                           |             |

| Bright    |                       |                           |             |

Table 2

| Variation | V <sub>R</sub> |

|-----------|----------------|

| Maximum   |                |

| Minimum   |                |

Table 3

| R at room   |  |

|-------------|--|

| temperature |  |

Table 4

| Variation | Vthermistor |

|-----------|-------------|

| Room Temp |             |

| Hot       |             |

#### Questions

- 1. If the LDR and resistor positions had been swapped, how would the values of Table 2 change?

- 2. Would the voltages measured in Table 2 change appreciably if R had been 1 k $\Omega$  instead of 10 k $\Omega$ ?

- 3. If the positions of the thermistor and resistor in Figure 2 had been swapped, how would the Table 5 values change?

- 4. If 20 volt power sources had been used, how would the values of Tables 2 and 5 change, if at all?

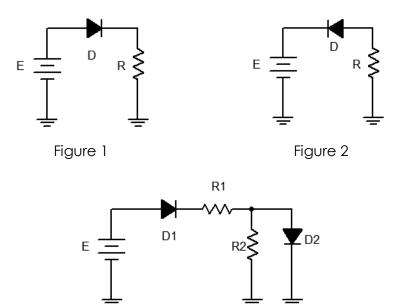

# 3 Diode Curves

## Objective

The objective of this exercise is to examine the operation of the basic switching diode and to plot its characteristic curve. Basic DC circuit operation will also be examined.

## Theory Overview

The basic diode is an asymmetric non-linear device. That is, its current-voltage characteristic is not a straight line and it is sensitive to the polarity of an applied voltage or current. When placed in forward bias (i.e. positive polarity from anode to cathode), the diode will behave much like a shorted switch and allow current flow. When reversed biased the diode will behave much like an open switch, allowing little current flow. Unlike a switch, a silicon diode will exhibit an approximate 0.7 volt drop when forward biased. The precise voltage value will depend on the semiconductor material used. This volt drop is sometimes referred to as the *knee voltage* as the resulting I-V curve looks something like a bent knee.

The effective instantaneous resistance of the diode above the turn-on threshold is very small, perhaps a few ohms or less, and is often ignored. Analysis of diode circuits typically proceeds by determining if the diode is forward or reversed biased, substituting the appropriate approximation for the device, and then solving for desired circuit parameters using typical analysis techniques. For example, when forward biased, a silicon diode can be thought of as a fixed 0.7 volt drop, and then KVL and KCL can be applied as needed. The polarity of the device is typically denoted by a band placed closest to the cathode.

## Equipment

| (1) Adjustable DC power supply                               | model:  | srn: |

|--------------------------------------------------------------|---------|------|

| (1) DMM                                                      | model:  | srn: |

| (2) Signal diodes (1N4148, 1N914)                            |         |      |

| (1) 1 k $\Omega$ resistor <sup>1</sup> / <sub>4</sub> watt   | actual: |      |

| (1) 10 k $\Omega$ resistor $\frac{1}{4}$ watt                | actual: |      |

| (1) 4.7 k $\Omega$ resistor <sup>1</sup> / <sub>4</sub> watt | actual: |      |

|                                                              |         |      |

1N4148/1N914 Datasheet: https://www.onsemi.com/pub/Collateral/1N914-D.PDF

#### **Schematics**

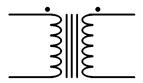

Figure 3

#### Procedure

#### Forward Curve

- 1. Consider the circuit of Figure 1 using  $R = 1 k\Omega$ . For any positive value of E, the diode should be forward biased. Once E exceeds the knee voltage, all of E (minus approximately 0.7 volts) drops across R. Thus, as E increases, so does the diode current.

- 2. Build the circuit of Figure 1 using  $R = 1 k\Omega$ . Set E to 0 volts and measure both the diode's voltage and current and record the results in Table 1. Remember, voltage is measured across a device (parallel) while current is measured through it (series). Repeat this process for the remaining source voltages listed.

- 3. From the data collected in Table 1, plot the current versus voltage characteristic of the forward biased diode. Make sure  $V_D$  is the horizontal axis with  $I_D$  on the vertical.

#### Reverse Curve

4. Consider the circuit of Figure 2 using  $R = 1 k\Omega$ . For any positive value of E, the diode should be reversed biased. In this case, the diode should always behave like an open switch and thus no current should flow. If no current flows, the voltage across R should be zero, and thus the diode voltage should be equal to the applied source voltage. Note that the diode's voltage polarity is negative with respect to that of Figure 1.

- 5. Build the circuit of Figure 2 using  $R = 1 k\Omega$ . Set E to 0 volts and measure both the diode's voltage and current and record the results in Table 2. Repeat this process for the remaining source voltages listed.

- 6. From the data collected in Table 2, plot the current versus voltage characteristic of the reverse biased diode. Make sure  $V_D$  is the horizontal axis with  $I_D$  on the vertical.

#### Practical Analysis

- 7. Consider the circuit of Figure 3 using E = 12 volts,  $R1 = 10 \text{ k}\Omega$  and  $R2 = 4.7 \text{ k}\Omega$ . Analyze the circuit using the ideal 0.7 volt forward drop approximation and determine the voltages across the two resistors. Record the results in the first two columns of the first row (Variation 1) of Table 3.

- 8. Build the circuit of Figure 3 using E = 12 volts,  $R1 = 10 \text{ k}\Omega$  and  $R2 = 4.7 \text{ k}\Omega$ . Measure the voltages across the two resistors. Record the results in columns three and four of the first row (Variation 1) of Table 3. Also compute and record the percent deviations in columns four and five.

- 9. Reverse the direction of D1 and repeat steps 7 and 8 as Variation 2 in Table 3.

- 10. Return D1 to the original orientation and reverse the direction of D2. Repeat steps 7 and 8 as Variation 3 in Table 3.

- 11. Reverse the direction of both D1 and D2, and repeat steps 7 and 8 as Variation 4 in Table 3.

#### **Computer Simulation**

12. Repeat steps 7 through 11 using a simulator, recording the results in Table 4.

## Data Tables

| E (volts) | V <sub>D</sub> | I <sub>D</sub> |

|-----------|----------------|----------------|

| 0         |                | 0              |

| 0.5       |                |                |

| 1         |                |                |

| 2         |                |                |

| 4         |                |                |

| 6         |                |                |

| 8         |                |                |

| 10        |                |                |

| E (volts) | V <sub>D</sub> | I <sub>D</sub> |

|-----------|----------------|----------------|

| 0         |                |                |

| 1         |                |                |

| 2         |                |                |

| 5         |                |                |

| 10        |                |                |

| 15        |                |                |

Table 2

| Variation | V <sub>R1 Theory</sub> | $V_{R2}$ Theory | V <sub>R1 Exp</sub> | V <sub>R2 Exp</sub> | % Dev V <sub>R1</sub> | $\%DevV_{\mbox{\tiny R2}}$ |

|-----------|------------------------|-----------------|---------------------|---------------------|-----------------------|----------------------------|

| 1         |                        |                 |                     |                     |                       |                            |

| 2         |                        |                 |                     |                     |                       |                            |

| 3         |                        |                 |                     |                     |                       |                            |

| 4         |                        |                 |                     |                     |                       |                            |

Table 3

| Variation | V <sub>R1 Sim</sub> | $V_{R2Sim}$ |

|-----------|---------------------|-------------|

| 1         |                     |             |

| 2         |                     |             |

| 3         |                     |             |

| 4         |                     |             |

#### Table 4

#### Questions

- 1. Is 0.7 volts a reasonable approximation for a forward bias potential? Is an open circuit a reasonable approximation for a reverse biased diode? Support your arguments with experimental data.

- 2. The "average" resistance of a forward biased diode can be computed by simply dividing the diode's voltage by its current. Using Table 1, determine the smallest average diode resistance (show work).

- 3. The instantaneous resistance (also known as AC resistance) of a diode may be approximated by taking the differences between adjacent current-voltage readings. That is,  $r_{diode} = \Delta V_{diode} / \Delta I_{diode}$ . What are the smallest and largest resistances using Table 1 (show work)? Based on this, what would a plot of instantaneous diode resistance versus diode current look like?

- 4. If the circuit of Figure 3 had been constructed with LEDs in place of switching diodes, would there be any changes to the values measured in Table 3? Why/why not?

## **4** Light Emitting Diodes

## Objective

This exercise examines the general performance and use of light emitting diodes. This includes forward bias and reverse bias characterization along with brightness variation.

## Theory Overview

The LED is similar to the ordinary signal or rectifying diode in that it is polarity sensitive. In reverse bias the device behaves as an open and prevents current flow. In forward bias, the device allows current flow once its forward barrier potential is reached. This potential is significantly higher than that of ordinary diodes and depends on the material used, and hence, the color that is displayed. Generally, luminous intensity is a function of the forward current. That is, the greater the current, the brighter the output. In operation, a series limiting resistor or other control device must be used to limit the forward current and prevent damage that could occur to the LED from excessive current. Different technologies are used in the design and production of LEDs and there are many variations including full spectrum (white) and high brightness versions. The cathode of an LED is typically denoted by a flat spot on the plastic casing and/or by the shorter of the two leads.

#### Equipment

| (1) Adjustable DC power supply                                         | model:  | srn: |  |

|------------------------------------------------------------------------|---------|------|--|

| (1) DMM                                                                | model:  | srn: |  |

| (1) Each of standard LEDs of various colors (red, blue, green, yellow) |         |      |  |

| (1) High brightness white LED                                          |         |      |  |

| (1) 1 k $\Omega$ resistor <sup>1</sup> / <sub>4</sub> watt             | actual: |      |  |

|                                                                        |         |      |  |

|                                                                        |         |      |  |

Standard red LED Datasheet:

https://www.sparkfun.com/datasheets/Components/LED/COM-09590-YSL-R531R3D-D2.pdf

High brightness white LED Datasheet:

http://cdn.sparkfun.com/datasheets/Components/General/YSL-R1042WC-D15.pdf

#### Schematics

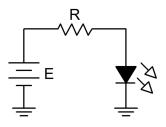

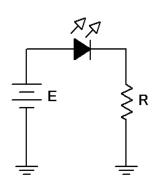

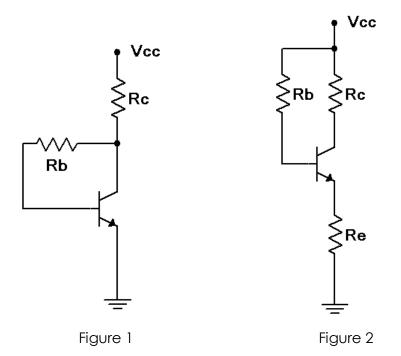

Figure 1

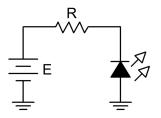

Figure 2

#### Procedure

#### Forward Curve

- 1. Consider the circuit of Figure 1 using  $R = 1 k\Omega$ . For any positive value of E, the diode should be forward biased. Once E exceeds the knee voltage, the difference between the source and the knee drops across R. Thus, as E increases, so does the LED current and hence its brightness.

- 2. Build the circuit of Figure 1 using  $R = 1 k\Omega$  and the red LED. Set E to 0 volts and measure both the LED voltage and current and record the results in Table 1. Note the relative brightness level. Repeat this process for the remaining source voltages listed.

- 3. From the data collected in Table 1, plot the current versus voltage characteristic of the forward biased LED. Make sure  $V_D$  is the horizontal axis with  $I_D$  on the vertical.

- 4. Repeat steps 2 and 3 for the blue LED using Table 2.

- 5. If other colors are available repeat steps 2 and 3 for them using Table 3 (create other tables as needed).

#### High Brightness

6. Replace the LED of Figure 1 with the high brightness white LED. Set the supply to 12 volts. Record the LED voltage, current and brightness in Table 4.

#### Reverse Curve

- 7. Consider the circuit of Figure 2 using  $R = 1 k\Omega$ . For any positive value of E, the LED should be reversed biased. In this case, the LED should always be open causing no current to flow. If no current flows, the LED produces no light. Also, the voltage across R should be zero, and thus the LED voltage should be equal to the applied source voltage. Note that the LED voltage polarity is negative with respect to that of Figure 1.

- 8. Build the circuit of Figure 2 using  $R = 1 k\Omega$  using the red LED. Set E to 0 volts and measure both the LED voltage and current and record the results in Table 5. Repeat this process for the remaining source voltages listed.

- 9. From the data collected in Table 5, plot the current versus voltage characteristic of the reverse biased diode. Make sure  $V_D$  is the horizontal axis with  $I_D$  on the vertical.

| E (volts) | V <sub>D</sub> | Ι <sub>D</sub> | Brightness |

|-----------|----------------|----------------|------------|

| 0         |                |                |            |

| 1         |                |                |            |

| 2         |                |                |            |

| 3         |                |                |            |

| 4         |                |                |            |

| 6         |                |                |            |

| 12        |                |                |            |

#### Data Tables

Table 1, Color: Red

| E (volts) | VD | ID | Brightness |

|-----------|----|----|------------|

| 0         |    |    |            |

| 1         |    |    |            |

| 2         |    |    |            |

| 3         |    |    |            |

| 4         |    |    |            |

| 6         |    |    |            |

| 12        |    |    |            |

Table 2, Color: Blue

| E (volts) | VD | ID | Brightness |

|-----------|----|----|------------|

| 0         |    |    |            |

| 1         |    |    |            |

| 2         |    |    |            |

| 3         |    |    |            |

| 4         |    |    |            |

| 6         |    |    |            |

| 12        |    |    |            |

Table 3, Color:

| E (volts) | V <sub>D</sub> | Ι <sub>D</sub> | Brightness |

|-----------|----------------|----------------|------------|

| 12        |                |                |            |

Table 4, High Brightness

| E (volts) | VD | Ι <sub>D</sub> |

|-----------|----|----------------|

| 0         |    |                |

| 1         |    |                |

| 3         |    |                |

| 8         |    |                |

#### Table 5

## Questions

- 1. Is the forward knee voltage of an LED comparable to that of ordinary switching and rectifying diodes?

- 2. Are the knee voltages of LEDs consistent across colors?

- 3. Compare the reverse characteristics of LEDs and switching diodes.

- 4. What can be said regarding LED brightness and current?

# 5 Photodiodes

## Objective

The objective of this exercise is to examine the operation of the photodiode in both the photovoltaic and photoconductive modes.

## Theory Overview

The photodiode is, in essence, the reverse of the LED. In fact, depending on their design, LEDs can be used as a type of photodiode. Photodiodes are responsive to light in one of two ways. The first method is the photovoltaic mode. In this mode, a voltage appears across the PN junction that is proportional to the amount of light striking it. It can be thought of as a small voltage source or battery. The second mode is photoconductive. In this mode, the photodiode is reverse biased by an external DC supply. The amount of current flowing through the diode will be proportional to the amount of light striking the junction. Typically, this current will pass through a series resistor to create a voltage or it can be sent into a current amplifier circuit.

A photo emitter/detector pair is a pairing of an LED and a photodiode that are designed to produce and detect the same wavelength of light. The wavelength of light may be outside the range of the human visible spectrum. Infrared (IR) is often used for consumer remote control devices. Emitter/detector pairs might use a phototransistor in place of a photodiode. The performance is similar except that photodiodes tend to have a quicker response while phototransistors tend to produce higher currents.

## Equipment

| (1) Adjustable DC power supply                                           | model:  | srn: |  |

|--------------------------------------------------------------------------|---------|------|--|

| (1) DMM                                                                  | model:  | srn: |  |

| (1) Non-diffuse light source (pen light)                                 |         |      |  |

| (1) Yellow LED                                                           |         |      |  |

| (1) Blue LED                                                             |         |      |  |

| (1) IR emitter/detector pair (Lite-On LTE-302 emitter, LTR-301 detector) |         |      |  |

| (1) 470 $\Omega$ resistor <sup>1</sup> / <sub>4</sub> watt               | actual: |      |  |

| (1) 33 k $\Omega$ resistor <sup>1</sup> / <sub>4</sub> watt              | actual: |      |  |

|                                                                          |         |      |  |

IR Emitter Datasheet: <u>http://optoelectronics.liteon.com/upload/download/DS-50-92-0009/E302.pdf</u> IR Detector Datasheet: <u>http://optoelectronics.liteon.com/upload/download/DS-50-93-0013/LTR-301.pdf</u>

#### Schematic

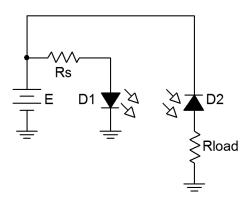

Figure 1

#### Procedure

#### LED as Detector

- Most LEDs can be used as light detectors. In photovoltaic mode, the output potential is a function of the light level and the make-up of the device (i.e., typically its color). Insert a yellow LED into a protoboard with nothing obstructing it. Place a DMM across it and measure the resulting DC voltage, recording it in Table 1 under "Normal".

- 2. Shade the LED so that minimal light strikes it and measure the resulting voltage. Record the value in Table 1 under "Dark".

- 3. Using the pen light, illuminate the LED from a distance of approximately 10 centimeters, measure and record the voltage in Table 1 under "Bright". Also, slowly vary the distance of the pen light from a few centimeters to 20 or so and note what happens to the voltage.

- 4. Replace the yellow LED with the blue LED and repeat steps 1 through 3.

#### IR Emitter/Detector Pair

- 5. Figure 1 shows an emitter/detector pair. These devices will emit and detect light at the same wavelength and tend to not produce or detect light at other wavelengths. This aids in avoiding interference. The detector is configured in photoconductive mode. Its current will increase with increasing light level. This current also flows through Rload meaning that Vload will be proportional to light level.

- 6. Build the circuit of Figure 1 using E = 7 volts,  $Rs = 470 \Omega$  and  $Rload = 33 k\Omega$ . The emitter diode is denoted with a yellow dot on its case while the detector diode shows a red dot. It is very important

that the pair properly be aligned. The bubbles should face each other and cases should be at same height, effectively aiming one bubble at the other. Further, they should only be a few millimeters apart. Finally, the short leads indicate the cathodes.

- 7. Energize the circuit. Because this pair operates in the infrared, nothing will be apparent to the human eye. Verify that the emitter is operating by measuring the voltage across it. It should be in the vicinity of 1.1 volts.

- 8. Measure Vload and record the value in Table 2.

- 9. Slip an opaque card such as a thin piece of black plastic or cardboard between the emitter/detector pair. Measure and record Vload in Table 2.

#### Data Tables

| Variation | V <sub>LED-YELLOW</sub> | V <sub>LED-BLUE</sub> |

|-----------|-------------------------|-----------------------|

| Normal    |                         |                       |

| Dark      |                         |                       |

| Bright    |                         |                       |

Table 1

| Variation | $V_{LOAD}$ |

|-----------|------------|

| Open      |            |

| Blocked   |            |

#### Questions

1. What is the effect of light intensity on the LED when used in photovoltaic mode?

2. What influence does the color of the LED have on the voltage produced when used in photovoltaic mode?

3. What is the correlation between Vload and light level in Figure 1? Give at least two examples of where this effect might be put to good use.

4. Why might an infrared emitter/detector system be used in consumer electronics in place of ordinary visible light emitter/detectors?

## 6 The Zener Diode

#### Objective

The objective of this exercise is to examine the operation of the Zener diode and to plot its characteristic curve.

#### Theory Overview

When forward biased, the Zener diode behaves similarly to an ordinary switching diode, that is, it incurs a 0.7 volt drop for silicon devices. Unlike a switching diode, the Zener is normally placed in reverse bias. If the circuit potential is high enough, the Zener will exhibit a fixed voltage drop. This is called the Zener potential or  $V_z$ . Manufacturer's specify this voltage with respect to the Zener test current, or  $I_{ZT}$ , a point past the knee of the voltage-current curve. That is, if the Zener's current is at least equal to  $I_{ZT}$ , then its voltage is approximately equal to the rated  $V_z$ . Above this current, even very large increases in current will produce only very modest changes in voltage. Therefore, for basic circuit analysis, the Zener can be replaced mathematically by a fixed voltage source equal to  $V_z$ . In practice, some series resistance is usually required to limit the current to a value below the Zener's maximum in order to prevent damage.

#### Equipment

| (1) Adjustable DC power supply                 | model:      | srn:  |

|------------------------------------------------|-------------|-------|

| (1) DMM                                        | model:      | _srn: |

| (1) Zener diode around 5.1 volts (NZX5         | V1B, 1N751) |       |

| (1) 2.2 k $\Omega$ resistor $\frac{1}{4}$ watt | actual:     |       |

| (1) 4.7 k $\Omega$ resistor $\frac{1}{4}$ watt | actual:     |       |

NZX5V1B Datasheet: <u>https://assets.nexperia.com/documents/data-sheet/NZX\_SER.pdf</u> 1N751 Datasheet: <u>http://www.digitroncorp.com/Documents/Datasheets/1N746-1N759A,-1N4370-1N4372A.aspx?ext=.pdf</u>

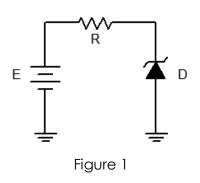

#### Schematics

Figure 2

#### Procedure

#### Reverse Curve

- 1. Consider the circuit of Figure 1 using  $R = 2.2 \text{ k}\Omega$ . For any positive value of E the Zener is reverse biased. Until the Zener potential is reached, the diode resistance is effectively infinite and thus no current flows. In this case the voltage across R is zero due to Ohm's law. Consequently, all of E should appear across the Zener. Once the source exceeds the Zener voltage, the remainder of E (i.e. E minus the Zener potential) drops across R. Thus, as E increases, the circulating current increases but the voltage across the zener remains steady.

- 2. Build the circuit of Figure 1 using  $R = 2.2 \text{ k}\Omega$ . Set E to 0 volts and measure both the diode's voltage and current and record the results in Table 1. Repeat this process for the remaining source voltages listed.

- 3. From the data collected in Table 1, plot the current versus voltage characteristic of the reverse biased diode. Make sure  $V_D$  is the horizontal axis with  $I_D$  on the vertical.

#### Practical Analysis

4. Consider the circuit of Figure 2 using  $R1 = 2.2 \text{ k}\Omega$  and  $R2 = 4.7 \text{ k}\Omega$ . In general, to analyze circuits like this, first assume that the Zener is out of the circuit and then compute the voltage across R2 using the voltage divider rule. If the resulting voltage is less than the Zener potential then the Zener is

inactive (high resistance) and does not affect the circuit. If, on the other hand, the resulting voltage is greater than the Zener potential then the Zener is active and will limit the voltage across R2 to  $V_z$ . Via KVL, the remainder of the voltage drops across R1 and from this the supply current may be determined. This current will then split between R2 and the Zener. The R2 current is found using Ohm's law. The Zener current is then found via KCL. Note that for higher and higher values of E, the voltage across (and therefore the current through) R2 does not change. Instead, all of the "excess" current from the source passes through the Zener.

- 5. Build the circuit of Figure 2 using  $R1 = 2.2 \text{ k}\Omega$  and  $R2 = 4.7 \text{ k}\Omega$ . Set E to 2 volts. Compute the theoretical diode voltage and current, and record them in the first row of Table 2. Then measure the diode current and voltage and record in Table 2. Finally, compute and record the deviations.

- 6. Repeat step 5 for the remaining source voltages in Table 2.

#### **Computer Simulation**

7. Repeat steps 5 and 6 using a simulator, recording the results in Table 3.

#### Data Tables

| E (volts) | VD | Ι <sub>D</sub> |

|-----------|----|----------------|

| 0         |    |                |

| 1         |    |                |

| 2         |    |                |

| 5         |    |                |

| 10        |    |                |

| 15        |    |                |

| 20        |    |                |

| E (volts) | $V_{DTheory}$ | D Theory | V <sub>D Exp</sub> | I <sub>D Exp</sub> | % Dev V <sub>D</sub> | % Dev I <sub>D</sub> |

|-----------|---------------|----------|--------------------|--------------------|----------------------|----------------------|

| 2         |               |          |                    |                    |                      |                      |

| 5         |               |          |                    |                    |                      |                      |

| 10        |               |          |                    |                    |                      |                      |

| 15        |               |          |                    |                    |                      |                      |

| 20        |               |          |                    |                    |                      |                      |

| E (volts) | $V_{DSim}$ | I <sub>D Sim</sub> |

|-----------|------------|--------------------|

| 2         |            |                    |

| 5         |            |                    |

| 10        |            |                    |

| 15        |            |                    |

| 20        |            |                    |

Table 3

#### Questions

1. Is it safe to assume that the voltage across a Zener is always equal to the rated  $V_Z$ ? Why/why not?

2. The instantaneous resistance (also known as AC resistance) of a diode may be approximated by taking the differences between adjacent current-voltage readings. That is,  $r_{diode} = \Delta V_{diode} / \Delta I_{diode}$ . What is the smallest effective resistance of the Zener using Table 1 (show work)?

3. If the circuit of Figure 1 had been constructed with the Zener flipped, how would this effect the results recorded in Table 1?

4. Assume that a diode with a much higher  $I_{ZT}$  rating (say, 100 mA) was used in this exercise. In general, what would the likely outcome be for the circuit of Figure 2?

# 7A The Oscilloscope (Tektronix MDO3000)

#### Objective

This exercise is of a particularly practical nature, namely, introducing the use of the oscilloscope. The various input scaling, coupling, and triggering settings are examined along with a few specialty features.

#### Theory Overview

The oscilloscope (or simply *scope*, for short) is arguably the single most useful piece of test equipment in an electronics laboratory. The primary purpose of the oscilloscope is to plot a voltage versus time although it can also be used to plot one voltage versus another voltage, and in some cases, to plot voltage versus frequency. Oscilloscopes are capable of measuring both AC and DC waveforms, and unlike typical DMMs, can measure AC waveforms of very high frequency (typically 100 MHz or more versus an upper limit of around 1 kHz for a general purpose DMM). It is also worth noting that a DMM will measure the RMS value of an AC sinusoidal voltage, not its peak value.

While the modern digital oscilloscope on the surface appears much like its analog ancestors, the internal circuitry is far more complicated and the instrument affords much greater flexibility in measurement. Modern digital oscilloscopes typically include measurement aides such as horizontal and vertical cursors or bars, as well as direct readouts of characteristics such as waveform amplitude and frequency. At a minimum, modern oscilloscopes offer two input measurement channels although four and eight channel instruments are increasing in popularity.

Unlike handheld DMMs, most oscilloscopes measure voltages with respect to ground, that is, the inputs are not floating and thus the black, or ground, lead is **always** connected to the circuit ground or common node. This is an extremely important point as failure to remember this may lead to the inadvertent short circuiting of components during measurement. The standard accepted method of measuring a non-ground referenced potential is to use two probes, one tied to each node of interest, and then setting the oscilloscope to subtract the two channels rather than display each separately. Note that this technique is not required if the oscilloscope has floating inputs (for example, in a handheld oscilloscope). Further, while it is possible to measure non-ground referenced signals by floating the oscilloscope itself through defeating the ground pin on the power cord, this is a safety violation and should not be done.

#### Equipment

| (1) DC power supply                         | model: | srn:   |

|---------------------------------------------|--------|--------|

| (1) Function generator                      | model: | _ srn: |

| (1) DMM                                     | model: | _srn:  |

| (1) Oscilloscope, Tektronix MDO 3000 series | model: | _srn:  |

#### Components

| (1) 10 kΩ | actual: |  |

|-----------|---------|--|

| (1) 33 kΩ | actual: |  |

#### Schematics and Diagrams

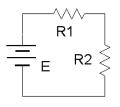

Figure 1

Figure 2

#### Procedure

- 1. Figure 1 is a photo of the face of a Tektronix MDO 3000 series oscilloscope. Compare this to the bench oscilloscope and identify the following elements:

- 1. Channel one through four BNC input connectors.

- 2. RF input connector and settings section.

- 3. Channel one through four select buttons.

- 4. Horizontal Scale (i.e., Sensitivity) and Position knobs.

- 5. Four Vertical Scale (i.e., Sensitivity) and Position knobs.

- 6. Trigger Level knob.

- 7. Math and Measure (in Wave Inspector) buttons.

- 8. Save button (below display).

- 9. *Autoset* button.

- 10. Menu Off button.

- 2. Note the numerous buttons along the bottom and side of the display screen. These menu buttons are context-sensitive and their function will depend on the most recently selected button or knob. Menus may be removed from the display by pressing the *Menu Off* button (multiple times for nested menus). Power up the oscilloscope. Note that the main display is similar to a sheet of graph paper. Each square will have an appropriate scaling factor or weighting, for example, 1 volt per division vertically or 2 milliseconds per division horizontally. Waveform voltages and timings may be determined directly from the display by using these scales.

- 3. Select the channel one and two buttons (yellow and blue) and also press the *Autoset* button. (Autoset tries to create reasonable settings based on the input signal and is useful as a sort of "panic button"). There should now be two horizontal lines on the display, one yellow and one blue. These traces may be moved vertically on the display via the associated Position knobs. Also, a trace can be removed by deselecting the corresponding channel button. The Vertical and Horizontal Scale knobs behave in a similar fashion and **do not** include calibration markings. That is because the settings for these knobs show up on the main display. Adjust the Scale knobs and note how the corresponding values at the bottom of the display change. Voltages are in a 1/2/5 scale sequence while Time is in a 1/2/4 scale sequence.

- 4. When an input is selected, a menu will pop up allowing control over that input's basic settings. One of the more important fundamental settings on an oscilloscope channel is the *Input Coupling*. This is controlled via one of the bottom row buttons. There are two choices: *AC* allows only AC signals through thus blocking DC, and *DC* allows **all** signals through (it does **not** prevent AC).

- 5. Set the channel one Vertical Scale to 5 volts per division. Set the channel two Scale to 2 volts per division. Set the Time (Horizontal) Scale to 1 millisecond per division. Finally, set the input Coupling to DC for both input channels and align the blue and yellow display lines to the center line of the display via the Vertical Position knob (note that pushing the vertical Position knobs will automatically center the trace).

- 6. Build the circuit of figure 2 using E=10 V, R1=10 kΩ and R2= 33kΩ. Connect a probe from the channel one input to the power supply (red or tip to the positive terminal, black clip to ground). Connect a second probe from channel two to R2 (again, red or tip to the high side of the resistor and the black clip to ground).

- 7. The yellow and blue lines should have deflected upward. Channel one should be raised two divisions (2 divisions at 5 volts per division yields the 10 volt source). Using this method, determine the voltage across R2 (remember, input two should have been set for 2 volts per division). Calculate the expected voltage across R2 using measured resistor values and compare the two in Table 1. Note that it is not possible to achieve extremely high precision using this method (e.g., four or more digits). Indeed, a DMM is often more useful for direct measurement of DC potentials. Double check the results using a DMM and the final column of Table 1.

- Select AC Coupling for the two inputs. The flat DC lines should drop back to zero. This is because AC Coupling blocks DC. This will be useful for measuring the AC component of a combined AC/DC signal, such as might be seen in an audio amplifier. Set the input coupling for both channels back to DC.

- 9. Replace the DC power supply with the function generator. Set the function generator for a one volt peak sine wave at 1 kHz and apply it to the resistor network. The display should now show two small sine waves. Adjust the Vertical Scale settings for the two inputs so that the waves take up the majority of the display. If the display is very blurry with the sine waves appearing to jump about side to side, the Trigger Level may need to be adjusted. Also, adjust the Time Scale so that only one or two cycles of the wave may be seen. Using the Scale settings, determine the two voltages (following the method of step 7) as well as the waveform's period and compare them to the values expected via theory, recording the results in Tables 2 and 3. Also crosscheck the results using a DMM to measure the RMS voltages.

- 10. To find the voltage across R1, the channel two voltage (voltage across R2) may be subtracted from channel one (E source) via the *Math* function. Use the red button to select the *Math* function and

create the appropriate expression from the menu (ch1 - ch2). This display shows up in red. To remove a waveform, press its button again. Remove the math waveform before proceeding to the next step.

- 11. One of the more useful aspects of the oscilloscope is the ability to show the actual waveshape. This may be used, for example, as a means of determining distortion in an amplifier. Change the waveshape on the function generator to a square wave, triangle, or other shape and note how the oscilloscope responds. Note that the oscilloscope will also show a DC component, if any, as the AC signal being offset or "riding on the DC". Adjust the function generator to add a DC offset to the signal and note how the oscilloscope display shifts. Return the function generator back to a sine wave and remove any DC offset.

- 12. It is often useful to take precise differential measurement on a waveform. For this, the bars or cursors are useful. Select the *Cursors* button toward the top of the oscilloscope. From the menu on the display, select *Vertical Bars*. Two vertical bars will appear on the display (it is possible that one or both could be positioned off the main display). They may be moved left and right via the Multipurpose knobs (next to the Cursors button). The *Select* button toggles between independent and tandem cursor movement. A read out of the bar values will appear in the upper portion of the display. They indicate the positions of the cursors, i.e., the location where they cross the waveform. Vertical Bars are very useful for obtaining time information as well as amplitudes at specific points along the wave. A similar function is the Horizontal Bars which are particularly useful for determining amplitudes. Try the Horizontal Bars by selecting them via the Cursors menu again (holding the *Cursors* button will bring up the menu).

- 13. For some waveform parameters, automatic readings are available. These are accessed via the *Measure* button. Press *Measure*, select *Add Measurement*, and page through the various options using the Multipurpose b knob. Select *Frequency*. Note that a small readout of the frequency will now appear on the display. Multiple measurements are possible simultaneously. **Important:** There are specific limits on the proper usage of these measurements. If the guidelines are not followed, erroneous values may result. Always perform an approximation via the Scale factor and divisions method even when using an automatic measurement!

- 14. Finally, a snap-shot of the screen may be saved for future work using the USB port and a USB memory stick via the *Save Menu* button. The pop up menu has options for saving the image as well as the trace data or setup info. Select *Save Screen Image* to save a bit mapped graphics file that can be used as is or processed further in a graphics program (for example, inverting the colors for printing). The .PNG format is recommended.

#### Data Tables

| V <sub>R2</sub> | Scale (V/Div) | Number of Divisions | Voltage Scope | Voltage DMM |

|-----------------|---------------|---------------------|---------------|-------------|

| Oscilloscope    |               |                     |               |             |

| Theory          | Х             | Х                   |               |             |

#### Table 1

|                              | Scale (V/Div) | Number of Divisions | Voltage Peak | Voltage RMS |

|------------------------------|---------------|---------------------|--------------|-------------|

| EOscilloscope                |               |                     |              |             |

| ETheory                      | Х             | Х                   |              |             |

| V <sub>R2</sub> Oscilloscope |               |                     |              |             |

| V <sub>R2</sub> Theory       | Х             | Х                   |              |             |

Table 2

|                       | Scale (S/Div) | Number of Divisions | Period | Frequency |

|-----------------------|---------------|---------------------|--------|-----------|

| <i>E</i> Oscilloscope |               |                     |        |           |

| ETheory               | Х             | Х                   |        |           |

# 7B The Oscilloscope (Tektronix TDS 3000)

#### Objective

This exercise is of a particularly practical nature, namely, introducing the use of the oscilloscope. The various input scaling, coupling, and triggering settings are examined along with a few specialty features.

#### Theory Overview

The oscilloscope (or simply *scope*, for short) is arguably the single most useful piece of test equipment in an electronics laboratory. The primary purpose of the oscilloscope is to plot a voltage versus time although it can also be used to plot one voltage versus another voltage, and in some cases, to plot voltage versus frequency. Oscilloscopes are capable of measuring both AC and DC waveforms, and unlike typical DMMs, can measure AC waveforms of very high frequency (typically 100 MHz or more versus an upper limit of around 1 kHz for a general purpose DMM). It is also worth noting that a DMM will measure the RMS value of an AC sinusoidal voltage, not its peak value.

While the modern digital oscilloscope on the surface appears much like its analog ancestors, the internal circuitry is far more complicated and the instrument affords much greater flexibility in measurement. Modern digital oscilloscopes typically include measurement aides such as horizontal and vertical cursors or bars, as well as direct readouts of characteristics such as waveform amplitude and frequency. At a minimum, modern oscilloscopes offer two input measurement channels although four and eight channel instruments are increasing in popularity.

Unlike handheld DMMs, most oscilloscopes measure voltages with respect to ground, that is, the inputs are not floating and thus the black, or ground, lead is **always** connected to the circuit ground or common node. This is an extremely important point as failure to remember this may lead to the inadvertent short circuiting of components during measurement. The standard accepted method of measuring a non-ground referenced potential is to use two probes, one tied to each node of interest, and then setting the oscilloscope to subtract the two channels rather than display each separately. Note that this technique is not required if the oscilloscope has floating inputs (for example, in a handheld oscilloscope). Further, while it is possible to measure non-ground referenced signals by floating the oscilloscope itself through defeating the ground pin on the power cord, this is a safety violation and should not be done.

#### Equipment

| (1) DC power supply                         | model: | srn:   |

|---------------------------------------------|--------|--------|

| (1) Function generator                      | model: | _ srn: |

| (1) DMM                                     | model: | _ srn: |

| (1) Oscilloscope, Tektronix TDS 3000 series | model: | _srn:  |

#### Components

| (1) 10 kΩ | actual: |

|-----------|---------|

| (1) 33 kΩ | actual: |

#### Schematics and Diagrams

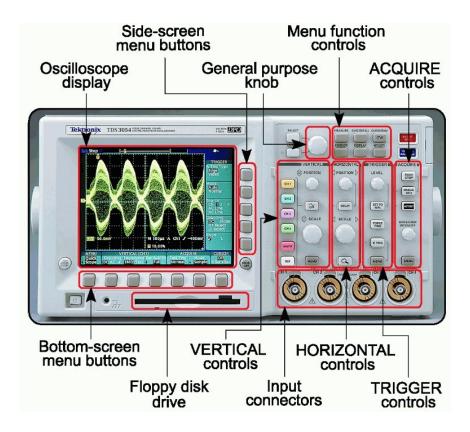

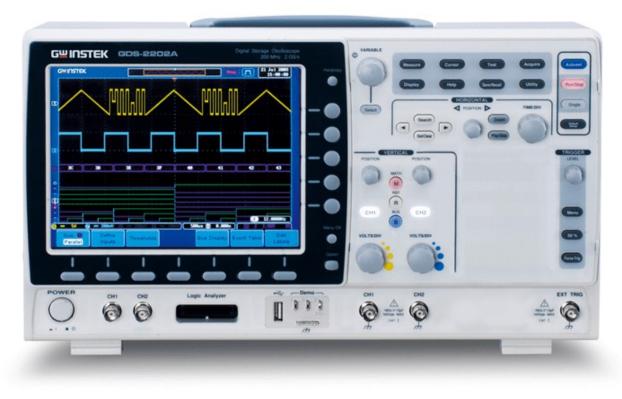

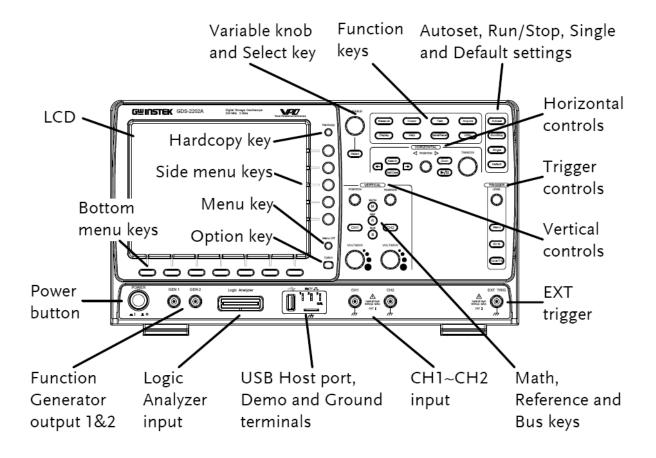

Figure 1A (Four channel version shown)

Figure 1B

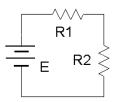

Figure 2

#### Procedure

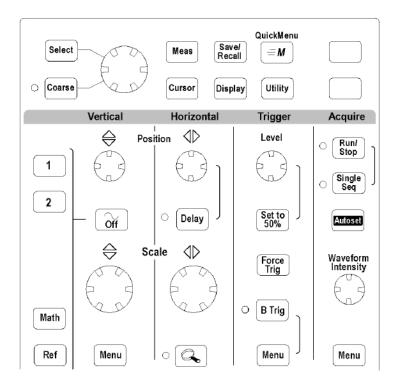

- 1. Figure 1 is an outline of the main face of a Tektronix TDS 3000 series oscilloscope. Compare this to the bench oscilloscope and identify the following elements:

- Channel one and two BNC input connectors.

- Trigger BNC input connector.

- Channel one and two select buttons.

- Horizontal sensitivity (or Scale) and Position knobs.

- Vertical sensitivity (or Scale) and Position knobs.

- Trigger Level knob.

- *Quick Menu* button.

- *Print/Save* button.

- *Autoset* button.

- 2. Note the numerous buttons along the bottom and side of the display screen. These buttons are context-sensitive and their function will depend on the mode of operation of the oscilloscope. Power up the oscilloscope and select the *Quick Menu* button. Notice that the functions are listed next to the buttons. This is a very useful menu and serves as a good starting point for most experiment setups. Note that the main display is similar to a sheet of graph paper. Each square will have an appropriate scaling factor or weighting, for example, 1 volt per division vertically or 2 milliseconds per division horizontally. Waveform voltages and timings may be determined directly from the display by using these scales.

- 3. Select the channel one and two buttons (yellow and blue) and also select the *Autoset* button. (Autoset tries to create reasonable settings based on the input signal and is useful as a sort of "panic button"). There should now be two horizontal lines on the display, one yellow and one blue. They may be moved via the Position knob. The Position knob moves the currently selected input (select the channel buttons alternately to toggle back and forth between the two inputs). The Vertical and Horizontal Scale knobs behave in a similar fashion and **do not** include calibration markings. That is because the settings for these knobs show up on the main display. Adjust the Scale knobs and note how the corresponding values in the display change. Voltages are in a 1/2/5 scale sequence while Time is in a 1/2/4 scale sequence.

- 4. One of the more important fundamental settings on an oscilloscope is the *Input Coupling*. This is controlled via one of the bottom row buttons. There are three choices: *Ground* removes the input thus showing a zero reference, *AC* allows only AC signals through thus blocking DC, and *DC* allows **all** signals through (it does **not** prevent AC).

- 5. Set the channel one Vertical Scale to 5 volts per division. Set the channel two Scale to 2 volts per division. Set the Time (Horizontal) Scale to 1 millisecond per division. Finally, set the input Coupling to Ground for both input channels and align the blue and yellow display lines to the center line of the display via the Vertical Position knob.

- 6. Build the circuit of Figure 2 using E=10 V,  $R1=10 \text{ k}\Omega$  and  $R2=33\text{k}\Omega$ . Connect a probe from the channel one input to the power supply (red or tip to plus, black clip to ground). Connect a second probe from channel two to R2 (again, red or tip to the high side of the resistor and the black clip to ground).

- 7. Switch both inputs to DC coupling. The yellow and blue lines should have deflected upward. Channel one should be raised two divisions (2 divisions at 5 volts per division yields the 10 volt source). Using this method, determine the voltage across R2 (remember, input two should have been set for 2 volts per division). Calculate the expected voltage across R2 using measured resistor values and compare the two in Table 1. Note that it is not possible to achieve extremely high precision using this method (e.g., four or more digits). Indeed, a DMM is often more useful for direct measurement of DC potentials. Double check the results using a DMM and the final column of Table 1.

- Select AC Coupling for the two inputs. The flat DC lines should drop back to zero. This is because AC Coupling blocks DC. This will be useful for measuring the AC component of a combined AC/DC signal, such as might be seen in an audio amplifier. Set the input coupling for both channels back to DC.

- 9. Replace the DC power supply with the function generator. Set the function generator for a one volt peak sine wave at 1 kHz and apply it to the resistor network. The display should now show two small sine waves. Adjust the Vertical Scale settings for the two inputs so that the waves take up the majority of the display. If the display is very blurry with the sine waves appearing to jump about side to side, the Trigger Level may need to be adjusted. Also, adjust the Time Scale so that only one or two cycles of the wave may be seen. Using the Scale settings, determine the two voltages (following the method of step 7) as well as the waveform's period and compare them to the values expected via theory, recording the results in Tables 2 and 3. Also crosscheck the results using a DMM to measure the RMS voltages.

- 10. To find the voltage across R1, the channel two voltage (voltage across R2) may be subtracted from channel one (E source) via the *Math* function. Use the red button to select the *Math* function and create the appropriate expression from the menu (ch1 − ch2). This display shows up in red. To remove a waveform, select it and then select *Off*. Remove the math waveform before proceeding to the next step.

- 11. One of the more useful aspects of the oscilloscope is the ability to show the actual waveshape. This may be used, for example, as a means of determining distortion in an amplifier. Change the

waveshape on the function generator to a square wave, triangle, or other shape and note how the oscilloscope responds. Note that the oscilloscope will also show a DC component, if any, as the AC signal being offset or "riding on the DC". Adjust the function generator to add a DC offset to the signal and note how the oscilloscope display shifts. Return the function generator back to a sine wave and remove any DC offset.

- 12. It is often useful to take precise differential measurement on a waveform. For this, the bars or cursors are useful. Select the *Cursor* button toward the top of the oscilloscope. From the menu on the display, select *Vertical Bars*. Two vertical bars will appear on the display (it is possible that one or both could be positioned off the main display). They may be moved left and right via the function knob (next to the Cursor button). The *Select* button toggles between the two cursors. A read out of the bar values will appear in the upper portion of the display. They indicate the positions of the cursors, i.e. the location where they cross the waveform. Vertical Bars are very useful for obtaining time information as well as amplitudes at specific points along the wave. A similar function is the Horizontal Bars which are particularly useful for determining amplitudes. Try the Horizontal Bars by selecting them via the *Cursor* button again.